Wireline Telecom

CMX683 – Call Progress and Voice Detector

Product description

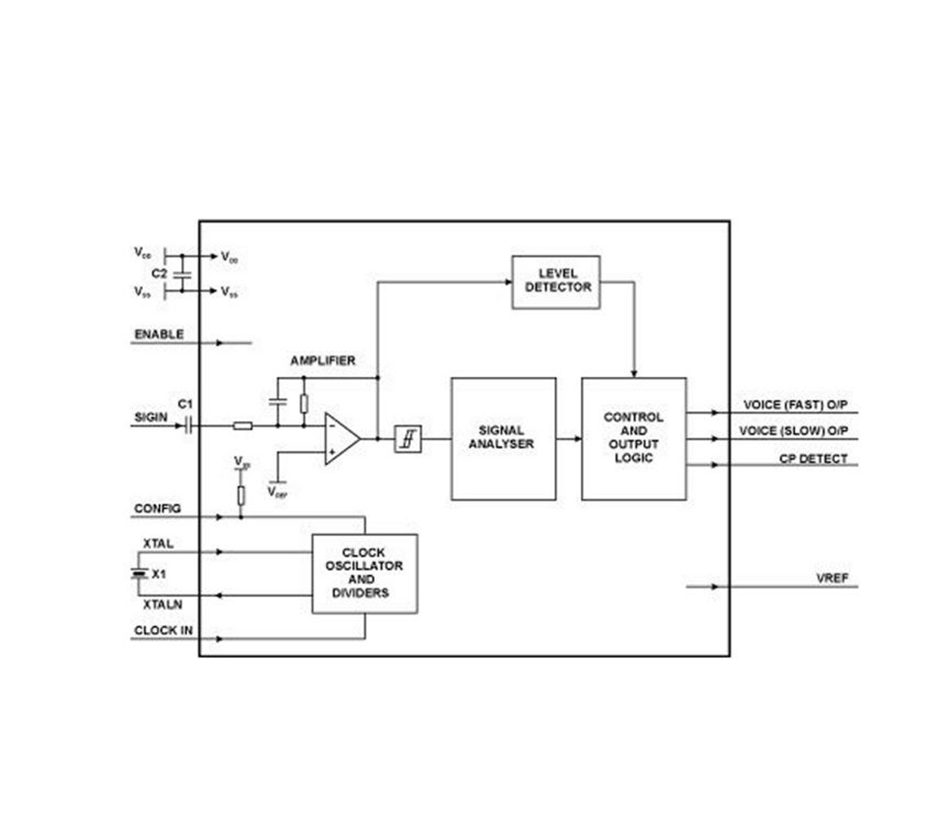

The CMX683 is a general purpose Call Progress tone detector for use in monitoring the progress of calls in Public Switched Telephone System (PSTN) applications.

Dial Tone, Ringing, Busy and Not Available states can be distinguished by using the host µC to qualify the cadence of the CP DETECT output.

The tone detector uses advanced digital techniques to characterise valid Call Progress tones, unwanted tones, line noise and voice or music signals. The CMX683 offers excellent sensitivity coupled with low false detection rates. The response time allows it to operate with almost any Call Progress system.

Voice mail messaging systems ‘stuttered dial tone’ is supported and it can distinguish voice or music activity from DTMF or Call Progress signals.

A single 3.58MHz crystal ensures accurate and repeatable performance and with supply requirements between 2.7V and 5.5V, and a low current consumption, the CMX683 can be easily integrated into a wide range of telecom equipment.

Devices are available through our Distributor Network.

Features

- Detects Single and Dual Call Progress Tones

- Worldwide Call Progress Tone Compatibility

- ‘Voice’ Detect Outputs (Fast and Slow)

- Wide Dynamic Range

- Low Falsing

- Low-Power Operation

(600µA at 3.0V)

Applications

- Worldwide Payphone Systems

- Telephone Redialing Systems

- Dialling Modems

- Banking and Billing Systems

- Telecom Test Equipment

- Telecom Security Systems

Power Supply Requirement

- 2.7 to 5.5 V

Design Resources

CMX683 FAQ

Q. Do you have a recommendation for how to best use the CP DETECT and VOICE FAST/SLOW outputs to detect call progress and voice activity?

A. All CMX683 outputs should be examined for cadence information. For example, sometimes a CP (Call Progress) signal will not cause the CP output to go high because the signal has a high harmonic content, or is amplitude or frequency modulated with another tone. Often this will result in ”voice” detection instead, so it is worth examining the VOICE FAST output for a regular CP cadence. Likewise, if you are only looking for “voice” activity, you may want to reduce host microprocessor load by examining the VOICE SLOW output first, which integrates the detection over a longer time. So the strategy could be:

TO DETECT CP TONES:

Examine CP cadence first, then examine VOICE FAST cadence. Ignore any output, which has an unexpected cadence. The longer the period over which the cadence can be checked, the better will be the result.

TO DETECT “VOICE” ACTIVITY:

Examine the VOICE FAST cadence first. If this is irregular it is probably “voice” activity. This can be confirmed by examining the VOICE SLOW output, which integrates the detection over a much longer period. If this output goes high and remains high for a long period of time, it is almost certainly “voice” activity. The longer the period over which the cadence can be checked, the better. If the cadence of the VOICE FAST output is regular, then see the item above.

The outputs are entirely dependent on the input signal. There is no maximum time for outputs remaining high.

You should configure the CMX683 external circuitry such that:

– Required SNR is met.

– Expected noise is kept BELOW detection threshold.

Anti-alias filter is implemented: signal energy at greater-than 10kHz has amplitude of less- than 38dBm (9.8mVrms).

Q.How does the CMX683 determine the difference between Voice Fast and Voice Slow?

A. The Voice Slow output is an integrated output (integrated over time) of the Voice Fast output with hysteresis switching.

The Voice Fast output is sampled every 5.75ms (6ms stated in the data sheet) and placed into a 128bit buffer. If Voice Fast=high=1 then a “1” is stored in the buffer and if Voice Fast=low =0 then a “0” is stored in the buffer.

So 5.7ms x 128bits=729ms (approx 728ms stated in the data sheet).

If the number of 1’s present in the buffer at any time goes over 64 (51% of the buffer size) then the Voice Slow=high=1.

If the number of 1’s present in the buffer at any time goes under 13 (10% of the buffer size) then the Voice Slow =low=0.

This switching process effect is called hysteresis. 51% and 10% have been selected by trial-and- error and decided-on to be the best-fit numbers. The threshold values of 10% and 51% cannot be adjusted.