Digital Voice

CMX639 – CVSD Voice Codec

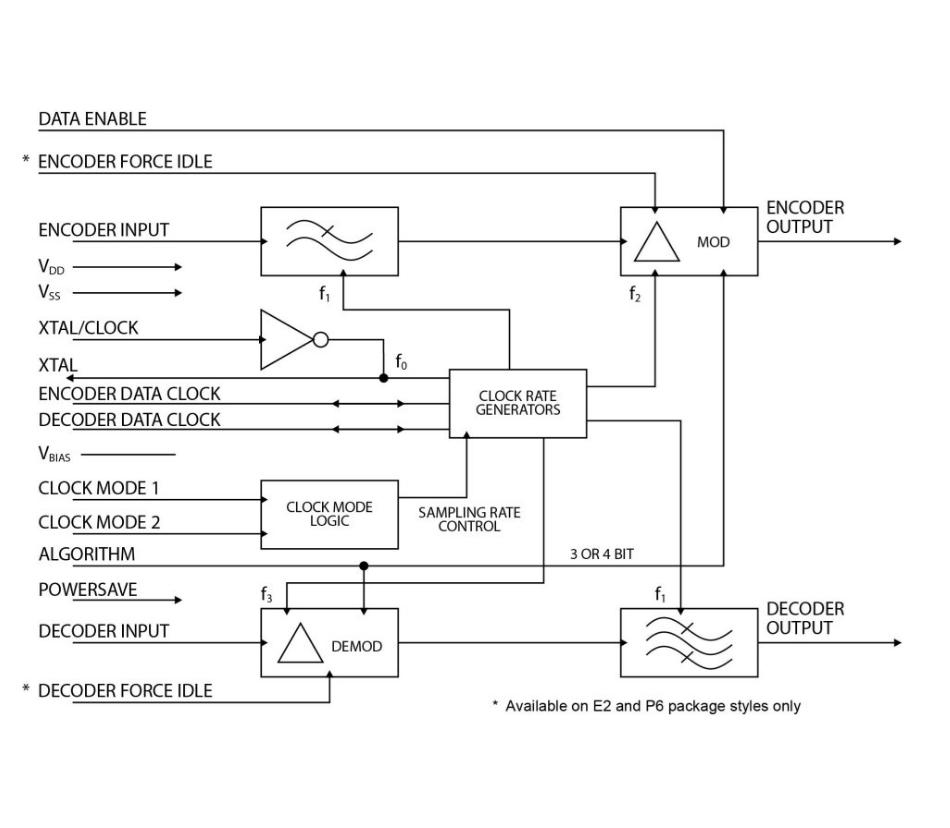

As a member of the CML DuraTALK® family of digital voice products, the CMX639 is a Continuously Variable Slope Delta modulation (CVSD) full duplex codec for use in consumer and commercial digital voice communication systems.

With its robust and selectable coding algorithms, low cost, very low power and small size, the CMX639 is ideal for use in a wide variety of consumer and business digital voice applications.

Its completely integrated CVSD Codec simplifies design and eliminates the costs, complexity and risk of external filters and software algorithms.

8kbps to 128kbps data/sampling clock rates are supported both via external clock signals or internally generated, programmable clocks. Internal data/sampling clocks are derived from a reference oscillator that uses an external clock crystal.

Devices are available through our Distributor Network.

Features

- Single Chip Full Duplex CVSD Codec

- On-Chip Input and Output Filters

- Programmable Sampling Clocks

- 3 or 4-Bit Compand algorithm

- Robust Coding for Wireless Links

- Encode and Decode Force-idle

- Separate Rx and Tx Paths

- Simple Control

Applications

- Consumer and Business Handheld Equipment

- Digital Voice Systems

- Spread Spectrum Wireless

- Cordless Phones

- Voice recording and storage

- Delay Lines

- Time domain Scramblers

- Multiplexers and Switches

Power Supply Requirement

- 3.0 to 5.5 V

Downloads

Design Resources

CMX639 FAQs

Q. The front of the data sheet mentions available sampling rates of 8kbps – 128kbps. Are these rates available for any crystal frequency?

A. No, they aren’t. The maximum external sampling rate should be one-half of the internal SCF clock rate. At a nominal crystal frequency of 1.024MHz, the internal SCF clock rate is 128kHz.

This translates to a maximum external sampling rate of 64kbps. If the crystal frequency is doubled to 2.048MHz, the internal SCF clock rate scales to 256kHz, and the resulting maximum recommended external sampling rate doubles to 128kbps. Please be aware that a change in crystal frequency from the rated 1.024MHz will result in proportional scaling of filter bandwidths, internally generated sampling rates (if used), etc.

Q. I am interested in establishing a voice link between a CMX639 and CMX649. How do I configure the CMX649 for this application?

A. While the CMX649 can perform CVSD voice coding through its first order integration, the CMX649 is not signal compatible with the CMX639, and hybrid systems using both devices should not be attempted.

Q. How do I choose between 3 or 4 bit companding?

A. The 3-bit algorithm yields better performance at lower sampling rates (32kbps and below).

For higher sampling rates (48kbps and above), the 4-bit algorithm will yield better performance.

Q. I am trying to use the CMX639 as a replacement for the Motorola MC3418 CVSD codec. What issues do I need to be aware of? (Note: these same issues apply to the Motorola MC34115 CVSD codec as well).

A. The MC3418 was a commercial FDX CVSD codec that had a fixed 4-bit companding algorithm. As long as the companding algorithm (3 or 4-bit), time constants (5ms for syllabic and 1ms for principle integrator in CMX639), and sampling rates are the same, a CMX639 design should be able to communicate with a MC3418 design.

Q. I am having trouble finding a 1.024MHz crystal for the CMX639. Any ideas where I can get one?

A. 1.024MHz crystals used to be popular but are becoming hard to find. Crystal manufacturers will still make them but they typically require a custom order; it is very difficult to find a standard off-the-shelf 1.024MHz crystal.

Off-the-shelf clock oscillators and VCXOs can be found for 1.024MHz, but they are typically more expensive than crystals.

An attractive alternative is to use a 2.048MHz or 4.096MHz crystal and use flip-flops to divide down to the desired speed. These crystals are readily available and relatively inexpensive.

Another alternative would be to use a 1.0MHz crystal. The sampling rates and filter bandwidths will change a little, but this will likely be an acceptable trade-off when considering the off-the-shelf status of 1.0MHz crystals. (If this is done, the customer will need to have control over both ends of the link!).

Q. I want to operate the CMX639 with external sampling clocks > 64kbps. How do I do this?

A. The internal switched-capacitor filter (SCF) clock is 128kHz when the crystal frequency is 1.024MHz. Even with externally provided sampling clocks, the chip’s ability to handle data is governed by its SCF clock speed. This means that any attempt to sample data at a rate >64kbps requires an increase in the SCF speed (to prevent aliasing), and this is done by increasing the crystal frequency. Therefore, to operate the CMX639 at a sampling rate of >64kbps with external sampling clocks, the crystal frequency must be increased.

The amount of crystal frequency increase depends on the desired sampling rate and the need to avoid aliasing (i.e. sampling rate needs to be less than half of the SCF rate). For 128kbps externally provided sampling rate, the crystal frequency needs to be doubled (2.048MHz) to allow for a SCF clock increase to 256kHz.

Note that an increase in the crystal frequency will cause the filter bandwidths to scale.

Q. My CMX639 design is noisier than I expected. What can I do to reduce the amount of noise in the circuit?

A. The CMX639 is capable of excellent CVSD audio quality. However, due to the fact that it can quantize very low amplitude speech signals (less than 10 mVrms), it is also sensitive to noise on VDD, VSS and VBIAS. This means careful attention must be paid to the printed circuit board design and layout.

If possible, the device should be completely surrounded with ground plane. In addition, low ESR capacitors should be used between VDD and VSS, as well as between VBIAS and VSS. Finally, the decoder output should be filtered with a simple RC network. The time constant for this network should be about 50 us (-3 dB frequency of approximately 3200 Hz). This will suppress high frequency clock noise coming from the decoder switched capacitor lowpass filter (the switched capacitor clock rate is nominally 128 KHz when the crystal frequency is set to 1.024 MHz).

The CMX639 decoder output driver is capable of driving resistive loads as low as 600 ohms. At the encoder input, we recommend a drive impedance of less than 1 Kohm. Regardless of the source impedance, there should be no resistor inserted between the source and the encoder input.